界面新闻记者 |

界面新闻编辑 | 文姝琪

由于在芯片生产中不可或缺,光刻机在世界各地构建本土半导体供应链时变得愈发重要。

来自荷兰的ASML一家公司就占据了全球八成以上的市场份额,其生产的光刻机当下常常一机难求,于是探索另一种技术路线、寻找替代性方案成为了行业公司自然而然的选择。

佳能就是其中的代表。这家日本相机巨头花二十年时间研发与ASML光刻路线不同的纳米压印技术,今年年初终于传出重要成果。

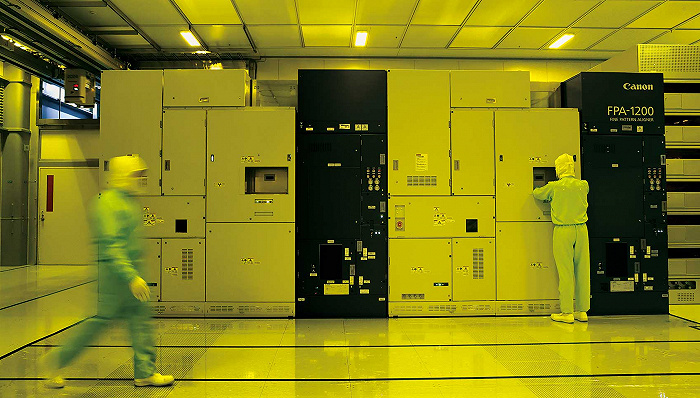

今年1月,据《金融时报》报道,日本佳能高管接受专访表示,公司最早将在今年量产自家的纳米压印半导体设备FPA-1200NZ2C。这款产品在去年10月首次亮相,对标的是ASML旗下制造7纳米以下先进制程芯片的EUV(极紫外光刻)光刻机。据公司介绍,其已经可以用来制造5纳米芯片,预计到2026年可实现2纳米。

但外界对此依然存有质疑。

半导体设备公司芯澈半导体创始人彭博方关注纳米压印技术在半导体领域的进展已有十多年。彭博方曾在上海微电子、ASML任职研发光刻及套刻测量技术近十年,在复旦大学任职期间又从事过纳米压印及化合物半导体检测技术的研究。在近期采访中,他对今年佳能量产的纳米压印光刻机仍抱持怀疑观望。

在他看来,最简单直接的评价标准就是看佳能产品上市后的客户订单。“如果佳能的产品今年量产后,东芝、SK海力士及更多与佳能宣布战略合作的厂商真正用它来生产芯片,并推向市场公开销售,才真正算是纳米压印实现量产的里程碑。” 彭博方对界面新闻记者说。

纳米压印与光刻是两种不同的技术路线。

两者的目标相同,简单描述就是将设计好的集成电路图“复制粘贴”到硅片上。而实现方法却大有不同,形象的比喻类似“照相”与“盖印章”。

光刻主要采用化学手段,利用紫外光辅以光刻胶等特殊化学品发生反应在硅片上“投影”出电路图。纳米压印则主要采用物理手段,利用制作好的集成电路图模板通过机械加压“复印”到硅片之上。

由于没有采用光刻中的投影成像原理,纳米压印省去了光刻机造价最昂贵的光学曝光机等成像系统,理论上认为是一种更低成本的方案。按照佳能产品负责人的说法,“纳米压印的价格将比EUV光刻机少一位数”,且耗电量只有光刻的十分之一。

ASML生产的EUV光刻机是全世界唯一能量产7纳米以下先进制程芯片的设备。今年1月,其又向外界首次公开展示了制造2纳米芯片的最新一代High NA EUV光刻机。

佳能希望纳米压印设备能够做到与其“共存”。而这一切的前提,都建立在佳能能否兑现量产诺言,真正将纳米压印技术推广至行业规模化生产芯片。

外界的存疑并不是毫无来由。

首先,纳米压印并不是一项新技术。相比于光刻在1961年被引入芯片生产用以造出第一台光刻机,纳米压印在半导体领域长期处于边缘位置。

1996年,普林斯顿电机系教授周郁(Stephen Chou)和学生在《Science》杂志上发表文章首次提出纳米压印技术。

与光刻机早早从最原始的接触式进化成非接触式不同,纳米压印采用机械加压方法必须接触。但实际接触过程中,纳米压印比光刻更容易出错,对准与缺陷问题始终是困扰纳米压印的两大难关。

半导体又恰恰对生产精度要求最苛刻,芯片尺寸越小容错率越低。纳米压印技术长期无法被证明应用于量产半导体领域10纳米以下先进制程芯片的能力。直至今天,相应制程芯片仍未大规模使用纳米压印技术生产。

佳能突破纳米压印技术讲的并不是一个新故事。

从2004年开始研究纳米压印,再到2014年收购美国纳米技术公司Molecular Imprints至今,几乎每年都会传出佳能纳米压印技术突破芯片生产尺寸的动向,以至于一家海外专门追踪佳能公司网站报道最新消息时,用的标题是“佳能的纳米压印来了(再次)”(Canon’s Nanoimprint Arrives (again))。

此外,佳能今年计划量产的产品与其2017年发布交付给东芝的纳米压印设备型号相同,按照当时宣传,其已经可以生产10纳米以下的芯片。至于如何从10纳米突破至5纳米、期间市场上为什么没有半导体厂商批量使用相关设备来生产芯片,佳能对外未作进一步解释说明。

彭博方告诉界面新闻记者,佳能近年来在解决对准问题上确实有了较大的进步,但纳米压印因缺陷问题造成的误差至今依旧没有看到有效解决方案,无法满足半导体行业对芯片良率的要求,至今无法应用于大规模生产。

纳米压印目前主要广泛应用于对制造缺陷容忍度较高的行业领域,比如光学和生物芯片,包括LED、AR设备、太阳能电池等等,但迄今为止都还未进入到大规模量产阶段。

评论