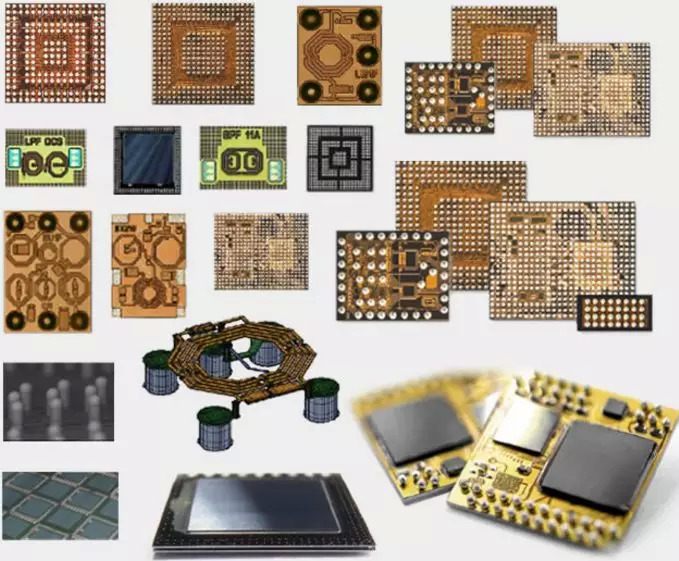

图片来源:长电科技官网

过去几年,半导体行业的关注点一直在于缩小特征尺寸来提高芯片性能,而现在的关注焦点已经转移到封装工艺上来。有数据表明,目前约有35%的芯片采用WLP技术封装,而市场的晶圆级封装(WLP)需求已经从引线键合转向倒装芯片封装。

2017年,封装厂商为推出更低成本的倒装芯片解决方案而延缓了扇出晶圆级封装(FOWLP)技术的使用,所以先进封装市场在2017年有所放缓。目前主流的先进封装技术以倒装芯片技术为核心,但FOWLP和3D IC封装技术也在不断发展。

市场上对高性能和小特征尺寸半导体的需求促进了先进封装技术的不断发展。未来外观更小的智能手机和高端服务器等终端设备将拥有更快的处理速度和更高I/O密度,这也意味着对封装工艺的技术要求将会越来越高。

IC制造中基本的互连和凸点工艺流程如下:阻挡/种子层沉积,图案化,电镀,光阻胶剥离和蚀刻。工程师们在设计倒装芯片时正逐步使用薄膜再分布技术(RDL),这项技术允许在无需更改I/O焊盘布局的条件下,将I/O焊盘重新分布到凸点焊盘。凸点底层金属(UBM)技术,能够在芯片上的(Cu或Al迹线)金属焊盘与焊料(或金)凸点之间形成一层金属化层,使得芯片与基板互连工艺更容易实现、互连可靠性更高。

封装互连可靠性和半导体性能的提升能带来I/O密度的提高,但这最终会导致线/间距几何形状、凸点直径和间距缩小。线/间距尺寸正在从10μm缩小到2μm,不久后凸点直径可能会缩减到10μm,光刻、光阻胶剥离和UBM/RDL蚀刻工艺步骤也会随之面临相关技术难题。

光阻胶剥离:一旦特征尺寸缩减,I/O密度增加,剥离光刻胶就会变得越来越难。光阻胶剥离工艺中,剥离剂扩散到光阻胶中发生溶胀得以去除光阻胶。而随着特征尺寸缩减,剥离剂能渗透光阻胶的能力受限,需要更长时间的喷涂才能达到较好的光刻胶剥离效果,势必会带来光阻胶剥离效率的降低从而影响产出。

能够保证光阻胶剥离效率的一种工艺方法是,在精准控制的加热和氮气环境下,将单张晶圆浸入到再循环溶剂蒸发槽中。考虑到下游的测序工序,需要确保每张晶圆浸入时间相同。在恰当化学成分的剥离剂和干膜厚度条件下,浸入过程可使高度交联的光阻剂发生溶胀和溶解。

浸入工序完成后,晶片表面在转移到单晶片旋转处理台期间需要保持剥离剂湿润;然后再使用高压化学风扇喷雾强力清除残留物,可确保晶圆表面完全没有光阻胶;最后再将晶片转移到旋转清洗干燥台完全清洁表面。

凸点底层金属/薄膜再分布技术(UBM/RDL):缩小的线和间距尺寸也带来了UBM/RDL蚀刻工艺的挑战。种子层蚀刻步骤的关键在于去除阻挡层和种子层的同时也要尽量减少底切。较高的底切会影响到器件的机械完整性,而不彻底的光阻胶剥离则会导致器件良率降低。而对于较大的特征尺寸,由于底切包含特征直径的一小部分,对器件的影响则会相对较小。相应地,如果特征尺寸从10μm缩小到1μm,相同的底切却会产生十倍的影响。为了尽量减少这过度蚀刻的问题,需要有更好的工艺控制来精确监测蚀刻步骤完成的时间,从而减少底切并保证临界特征(线或凸点)尺寸。

湿法蚀刻是各向同性工艺,横向蚀刻速率等于纵向蚀刻速率。蚀刻工艺中,只要达到了最小化的底切金属厚度,工艺需要立即停止。与湿式工作台中的批量处理相比,单晶片湿法处理(即一次刻蚀一个晶片)能更好地控制蚀刻工艺。与此同时,使用终点检测(EPD)也能为精准的金属蚀刻工艺终点提供原位自适应工艺流程控制,通过精准控制化学品供应时段分布来保证晶圆蚀刻的均匀性。

先进封装是未来封装的必然趋势。汽车电子产品包括自动驾驶辅助系统(ADAS),数据处理,5G基础设施部署对增强移动性和连通性有更多要求,智能手机和其他移动设备也在增加设备的功能性,这意味着终端产品的性能需求会持续影响封装市场。虽然FOWLP和3D集成等先进技术在当前市场上占比不到10%,但预计未来几年复合年增长率将超过15%。许多封装厂商正在以改进工艺流程和设备等方法和转变策略来解决技术难题,芯片制造厂商也需做好充分准备才能积极应对市场变化。

图片声明:如果我们使用了您的图片,请作者与本站联系索取稿酬。如您不希望作品出现在本站,可联系我们要求撤下您的作品。

评论